-

资源简介

《一种全摆幅CMOS自举采样开关研究》是一篇探讨CMOS电路设计中关键组件——自举采样开关的论文。该研究旨在解决传统采样开关在高速、高精度应用中所面临的限制,特别是在信号幅度和开关速度方面的不足。通过引入自举技术,该论文提出了一种新型的CMOS自举采样开关结构,以实现全摆幅的输入信号处理能力。

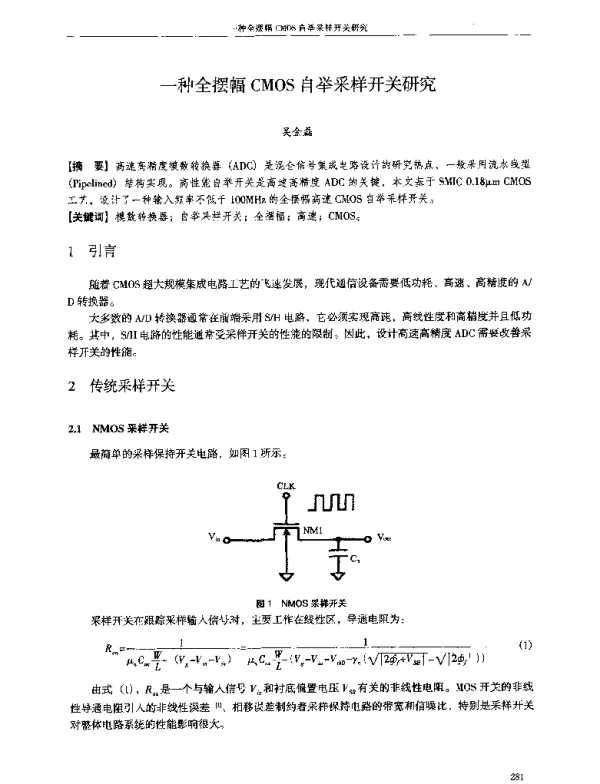

在现代集成电路设计中,采样开关是模数转换器(ADC)和数模转换器(DAC)中的重要组成部分。其主要功能是在特定时间点对输入信号进行采样,并保持该信号值以便后续处理。然而,传统的CMOS采样开关在工作过程中可能会受到寄生电容和阈值电压的影响,导致信号失真或无法完全捕捉输入信号的全范围。

为了解决这些问题,该论文提出了基于自举技术的改进方案。自举技术是一种利用内部电荷泵来提升控制信号电压的方法,从而使得开关能够更有效地导通和关断。这种方法可以显著提高开关的导通电阻性能,同时减少信号传输过程中的非线性失真。

论文详细分析了自举采样开关的工作原理,并对其电路结构进行了优化设计。通过合理选择晶体管尺寸和布局,该设计能够在不增加额外电源的情况下实现更高的电压摆幅。此外,研究还讨论了自举电容的选择和充电机制,以确保开关在高频操作下的稳定性。

为了验证设计的有效性,作者进行了仿真和实验测试。结果表明,所提出的自举采样开关在输入信号幅度接近电源电压时仍能保持良好的性能,且具有较低的导通电阻和较高的开关速度。这使得该设计特别适用于高速ADC等应用场景。

论文还比较了不同类型的采样开关结构,包括传统的CMOS开关、使用二极管连接的开关以及基于自举技术的开关。通过对比各项性能指标,如开关时间、导通电阻、功耗和信号失真度,作者证明了自举采样开关在多个方面均优于传统结构。

在实际应用中,全摆幅CMOS自举采样开关可以广泛用于通信系统、医疗设备、工业自动化等领域。特别是在需要高精度和高速度的场合,这种设计能够提供更可靠和稳定的信号采集能力。此外,由于其结构简单且易于集成,该设计也具备良好的可扩展性和适应性。

该论文不仅为CMOS采样开关的设计提供了新的思路,也为高速模拟信号处理电路的发展提供了理论支持和技术参考。通过深入研究自举技术的应用,作者展示了如何在有限的资源下实现高性能的电路设计。

综上所述,《一种全摆幅CMOS自举采样开关研究》是一篇具有较高学术价值和实用意义的论文。它不仅推动了CMOS采样开关技术的进步,也为相关领域的工程实践提供了重要的指导。随着电子技术的不断发展,这类高效、可靠的采样开关将在未来的集成电路设计中发挥越来越重要的作用。

-

封面预览

-

下载说明

预览图若存在模糊、缺失、乱码、空白等现象,仅为图片呈现问题,不影响文档的下载及阅读体验。

当文档总页数显著少于常规篇幅时,建议审慎下载。

资源简介仅为单方陈述,其信息维度可能存在局限,供参考时需结合实际情况综合研判。

如遇下载中断、文件损坏或链接失效,可提交错误报告,客服将予以及时处理。